# MIPS32® Architecture for Programmers VolumeIV-f: The MIPS® MT Application-Specific Extension to the MIPS32® Architecture

Document Number: MD00378 Revision 1.04 June 25, 2008

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2005-2007,2008 MIPS Technologies Inc. All rights reserved.

Copyright © 2005-2007,2008 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS-3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 24K, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, R3000, R4000, R5000, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, Corextend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, OCI, PDtrace, the Pipeline, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it, System Navigator, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

Template: nB1.03, Built with tags: 2B ARCH MIPS32

# **Table of Contents**

| Table of Contents                                               | 3  |

|-----------------------------------------------------------------|----|

| List of Figures                                                 | 5  |

| List of Tables                                                  | 6  |

| Chapter 1: Introduction to the MIPS® MT Architecture Extension  | 7  |

| 1.1: Background                                                 |    |

| 1.2: Definitions and General Description                        | 7  |

| Chapter 2: MIPS® MT Multithreaded Execution and Exception Model | 9  |

| 2.1: Multithreaded Execution                                    | g  |

| 2.2: MIPS® MT Exception Model                                   | g  |

| 2.3: New Exception Conditions                                   | g  |

| 2.4: New Exception Priority                                     |    |

| 2.5: Interrupts                                                 |    |

| 2.6: Bus Error Exceptions                                       |    |

| 2.7: Cache Error Exceptions                                     |    |

| 2.8: EJTAG Debug Exceptions                                     |    |

| 2.9: Shadow Register Sets                                       | 12 |

| Chapter 3: MIPS® MT Instructions                                |    |

| 3.1: New Instructions                                           |    |

| DMT                                                             |    |

| DVPE                                                            |    |

| EMT                                                             |    |

| EVPE                                                            |    |

| FORK                                                            |    |

| MFTR                                                            |    |

| MTTR                                                            |    |

| YIELD                                                           | 28 |

| Chapter 4: MIPS® MT Privileged Resource Architecture            | 31 |

| 4.1: Privileged Resource Architecture for MIPS® MT              |    |

| 4.2: MVPControl Register (CP0 Register 0, Select 1)             |    |

| 4.3: MVPConf0 Register (CP0 Register 0, Select 2)               |    |

| 4.4: MVPConf1 Register (CP0 Register 0, Select 3)               |    |

| 4.5: VPEControl Register (CP0 Register 1, Select 1)             |    |

| 4.6: VPEConf0 Register(CP0 Register 1, Select 2)                |    |

| 4.7: VPEConf1 Register(CP0 Register 1, Select 3)                |    |

| 4.8: YQMask Register (CP0 Register 1, Select 4)                 |    |

| 4.9: VPESchedule Register (CP0 Register 1, Select 5)            |    |

| 4.10: VPEScheFBack Register (CP0 Register 1, Select 6)          |    |

| 4.11: VPEOpt Register (CP0 Register 1, Select 7)                |    |

| 4.12: TCStatus Register (CP0 Register 2, Select 1)              |    |

| 4.13: TCBind Register (CP0 Register 2, Select 2)                | 48 |

|    | 4.14: TCRestart Register (CP0 Register 2, Select 3)                                              | . 49 |

|----|--------------------------------------------------------------------------------------------------|------|

|    | 4.14.1: Special Handling of the TCRestart Register in Processors that Implement the MIPS16e™ ASE | . 49 |

|    | 4.15: TCHalt Register (CP0 Register 2, Select 4)                                                 |      |

|    | 4.16: TCContext Register (CP0 Register 2, Select 5)                                              |      |

|    | 4.17: TCSchedule Register (CP0 Register 2, Select 6)                                             |      |

|    | 4.18: TCScheFBack Register (CP0 Register 2, Select 7)                                            |      |

|    | 4.19: SRSConf0 (CP0 Register 6, Select 1)                                                        |      |

|    | 4.20: SRSConf1 (CP0 Register 6, Select 2)                                                        |      |

|    | 4.21: SRSConf2 (CP0 Register 6, Select 3)                                                        |      |

|    | 4.22: SRSConf3 (CP0 Register 6, Select 4)                                                        |      |

|    | 4.23: SRSConf4 (CP0 Register 6, Select 5)                                                        |      |

|    | 4.24: Modifications to Existing MIPS® Privileged Resource Architecture                           |      |

|    | 4.24.1: SRSCtl Register                                                                          |      |

|    | 4.24.2: Cause Register                                                                           |      |

|    | 4.24.3: Machine Check Exceptions                                                                 |      |

|    | 4.24.4: Debug Register                                                                           |      |

|    | 4.24.5: EBase Register                                                                           |      |

|    | 4.24.6: Config1 Register                                                                         |      |

|    | 4.24.7: Config3 Register                                                                         |      |

|    | 4.26: Thread Allocation and Initialization Without FORK                                          |      |

|    | 4.27: Thread Termination and Deallocation without YIELD.                                         |      |

|    | 4.28: Multithreading and Coprocessors                                                            |      |

|    | 4.20. Wulltimoduling and Coprocessors                                                            | . 00 |

| Cŀ | apter 5: MIPS® MT Restrictions on MIPS32 Implementation                                          | 65   |

| 0. | 5.1: WAIT Instructions                                                                           |      |

|    | 5.2: SC Instructions                                                                             |      |

|    | 5.3: LL Instructions                                                                             |      |

|    | 5.4: SYNC Instructions                                                                           |      |

|    |                                                                                                  |      |

| Cŀ | apter 6: Multiple Virtual Processors in MIPS® MT                                                 | 67   |

| •  | 6.1: Multi-VPE Processors                                                                        | . 67 |

|    | 6.2: Reset and Virtual Processor Configuration                                                   |      |

|    | 6.3: MIPS® MT and Cache Configuration                                                            |      |

|    | <b>9</b>                                                                                         |      |

| Cŀ | apter 7: Data-Driven Scheduling of MIPS® MT Threads                                              | .71  |

| -  | 7.1: Gating Storage                                                                              |      |

|    |                                                                                                  |      |

| Cŀ | apter 1: EJTAG and MIPS® MT                                                                      | . 73 |

| •  | 1.2: EJTAG Debug Resources                                                                       |      |

|    | 1.3: Debug Exception Handling                                                                    |      |

|    |                                                                                                  |      |

| Δr | pendix A: Inter-Thread Communication Storage                                                     | 75   |

| ~l | A.1: Basic Concepts                                                                              |      |

|    | A.2: An ITC Storage Reference Model                                                              |      |

|    | A.3: Multiprocessor/Multicore ITC                                                                |      |

|    | A.4: Interaction with EJTAG Debug Facilities                                                     |      |

|    |                                                                                                  | •    |

|    | nendix B. Revision History                                                                       | 79   |

# **List of Figures**

| Figure 4.1: MVPControl Register Format   |    |

|------------------------------------------|----|

| Figure 4.2: MVPConf0 Register Format     | 35 |

| Figure 4.3: MVPConf1 Register Format     | 36 |

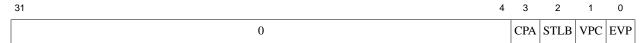

| Figure 4.4: VPEControl Register Format   | 37 |

| Figure 4.5: VPEConf0 Register Format     | 38 |

| Figure 4.6: VPEConf1 Register Format     | 40 |

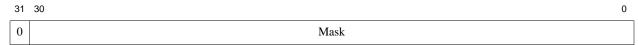

| Figure 4.7: YQMask Register Format       |    |

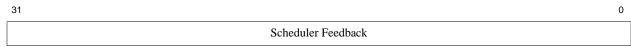

| Figure 4.8: VPESchedule Register Format  |    |

| Figure 4.9: VPEScheFBack Register Format | 43 |

| Figure 4.10: VPEOpt Register Format      | 44 |

| Figure 4.11: TCStatus Register Format    |    |

| Figure 4.12: TCBind Register Format      | 48 |

| Figure 4.13: TCRestart Register Format   | 49 |

| Figure 4.14: TCHalt Register Format      | 51 |

| Figure 4.15: TCContext Register Format   | 52 |

| Figure 4.16: TCSchedule Register Format  | 53 |

| Figure 4.17: TCScheFBack Register Format | 54 |

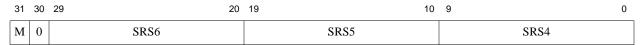

| Figure 4.18: SRSConf0 Register Format    |    |

| Figure 4.19: SRSConf1 Register Format    | 57 |

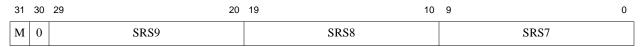

| Figure 4.20: SRSConf2 Register Format    |    |

| Figure 4.21: SRSConf3 Register Format    | 59 |

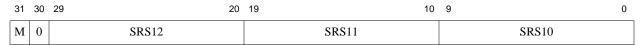

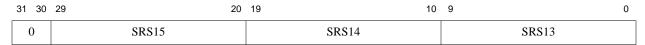

| Figure 4.22: SRSConf4 Register Format    |    |

# **List of Tables**

| Table 2.1: Priority of Exceptions in MIPS® MT              | 10 |

|------------------------------------------------------------|----|

| Table 3.1: MFTR Source Decode                              | 22 |

| Table 3.2: MTTR Destination Decode                         | 25 |

| Table 4.1: MIPS® MT PRA                                    | 31 |

| Table 4.2: MVPControl Register Field Descriptions          | 33 |

| Table 4.3: MVPConf0 Register Field Descriptions            | 35 |

| Table 4.4: MVPConf1 Register Field Descriptions            | 36 |

| Table 4.5: VPEControl Register Field Descriptions          | 37 |

| Table 4.6: VPEConf0 Register Field Descriptions            | 38 |

| Table 4.7: VPEConf1 Register Field Descriptions            | 40 |

| Table 4.8: YQMask Register Field Descriptions              |    |

| Table 4.9: VPEOpt Register Field Descriptions              | 44 |

| Table 4.10: TCStatus Register Field Descriptions           | 46 |

| Table 4.11: TCBind Register Field Descriptions             | 48 |

| Table 4.12: TCRestart Register Field Descriptions          | 49 |

| Table 4.13: TCHalt Register Field Descriptions             | 51 |

| Table 4.14: SRSConf0 Register Field Descriptions           | 55 |

| Table 4.15: SRSConf1 Register Field Descriptions           | 57 |

| Table 4.16: SRSConf2 Register Field Descriptions           | 58 |

| Table 4.17: SRSConf3 Register Field Descriptions           | 59 |

| Table 4.18: SRSConf4 Register Field Descriptions           | 60 |

| Table 4.19: MIPS® MT Thread Exception                      |    |

| Table 4.20: New Config3 Fields for MIPS® MT                | 62 |

| Table 4.21: TC State as Function of MIPS® MT PRA State     |    |

| Table 6.1: Dynamic Virtual Processor Configuration Options | 68 |

| Table A.1: ITC Reference Cell Views                        | 75 |

## Introduction to the MIPS® MT Architecture Extension

## 1.1 Background

Multithreading, or the concurrent presence of multiple active threads or contexts of execution on the same CPU, is an increasingly widely-used technique for tolerating memory and execution latency and for getting higher utilization out of processor functional units. The MIPS® Multithreading (MT) ASE is an extension to Release 2 of the MIPS32® Architecture which provides a framework for multithreading the MIPS processor architecture.

## 1.2 Definitions and General Description

A *thread context*, for the purposes of this document, is a collection of processor state necessary to describe the state of execution of an instruction stream in the MIPS32 Instruction Set Architecture. It includes a set of general purpose registers (GPRs), the MIPS Hi/Lo multiplier result registers, some internal representation of a program counter, and some associated MIPS32 privileged system coprocessor (CP0) state, specifically:

- The CU3..CU0, MX, and KSU fields of the CP0 Status register

- The ASID field of the CP0 EntryHi register.

- The SSt and OffLine fields of the EJTAG Debug register.

- The CP0 UserLocal register, if implemented.

A thread context also contains some new privileged resource state, to allow software to manage the new multithreading capabilities. Thread Context will be abbreviated as *TC*, both in the interests of brevity, and to minimize the confusion between a TC as state/storage and a thread of execution as a sequence of instructions.

A *processor context* is a larger collection of processor state, which includes at least one TC, but also the CP0 and system state necessary to describe an instantiation of the full MIPS32 Privileged Resource Architecture.

The MIPS MT ASE allows two distinct, but not mutually-exclusive, multithreading capabilities. A single MIPS processor or core can contain some number of *Virtual Processing Elements* (VPEs), each of which supports at least one thread context. To software, an *N* VPE processor looks like an *N*-way symmetric multiprocessor. All legacy MIPS32 read-write CP0 state must be implemented per-VPE. This allows existing SMP-capable operating systems to manage the set of VPEs, which transparently share the processor's execution units and other resources. A processor or core implementing multiple MIPS MT VPEs is referred to as a *Virtual Multiprocessor*, or VMP.

Each VPE can also contain some number of TCs beyond the single TC implicitly required by the base architecture. Multi-threaded VPEs require explicit operating system support, but with such support they provide a lightweight, fine-grained multithreaded programming model wherein threads can be created and destroyed, without operating system intervention in the typical cases, using new FORK and YIELD instructions, and where system service threads can be scheduled in response to external events with zero interrupt latency.

#### Introduction to the MIPS® MT Architecture Extension

A TC may be in one of two allocation states, *free* or *activated*. A **free** TC has no valid content and cannot be scheduled to issue instructions. An **activated** TC will be scheduled according to the implemented policies to fetch and issue instructions from its program counter. Only activated TCs may be scheduled. Only free TCs may be allocated to create new threads. Allocation and deallocation of TCs may be done explicitly by privileged software, or automatically via FORK and YIELD instructions which can be executed in user mode. Only TCs which have been explicitly designated as *Dynamically Allocatable* (DA) may be allocated or deallocated by FORK and YIELD.

An activated TC may be *running* or *blocked*. A **running** TC will fetch and issue instructions according to the thread scheduling policy in effect for the processor. Any or all running TCs may have instructions in the pipeline of a processor at a given point of time, but it is not knowable to software precisely which ones. A **blocked** TC is one which has issued an instruction which performs an explicit synchronization that has not yet been satisfied. While a running, activated TC may be stalled momentarily due to functional unit delays, memory load dependencies, or scheduling rules, its instruction stream will advance on its own within the limitations of the pipeline implementation. The instruction stream of a blocked TC cannot advance without some change in system state being effected by another thread or by external hardware, and as such it may remain blocked for an unbounded period of time.

Independently of whether it is free or activated, a TC may be *halted*. A **halted** TC is inhibited from being allocated by a FORK instruction, even if free, and inhibited from fetching and issuing instructions, even if activated. Only a TC in a halted state is guaranteed to be stable as seen by other TCs. Multithreaded execution may be temporarily inhibited on a VPE due to exceptions or explicit software interventions, but the activated threads that are inhibited in such cases are considered to be *suspended*, rather than implicitly halted. A **suspended** thread is inhibited from any action which might cause exceptions or otherwise change global VPE privileged resource state, but, unlike a halted thread, it may still have instructions active in the pipeline, and its internal TC state, including GPR values, may still be unstable.

And independently of whether an activated TC is halted, it will not be scheduled to fetch or issue if it has been set *offline* by code executing in EJTAG Debug mode, via the *OffLine* bit of the *Debug* register (see the EJTAG specification).

If executing in a sufficiently privileged mode, one TC can access another TC's register state, via new instructions to move to/from the registers of a "target" TC.

To allow for fine-grain synchronization of cooperating threads, an inter-thread communication (ITC) memory space can be created in virtual memory, with gating storage semantics to allow threads to be blocked on loads or stores until data has been produced or consumed by other threads. These gating storage semantics can also be applied to I/O devices such as FIFOs to provide a data-driven execution model.

The thread creation/destruction, and synchronization capabilities function without operating system intervention in the general case, but the resources they manipulate are all virtualizable via an operating system. This allows the execution of multithreaded programs with more "virtual" threads than there are TCs on a VPE, and for the migration of threads to balance load in multiprocessor systems. At any particular point in its execution, a thread is bound to a particular TC on a particular VPE. The number of that TC provides a unique identifier *at that point in time*. But context switching and migration can cause a single sequential thread of execution to have a series of different TCs, possibly on a series of different VPEs.

Dynamic binding of TCs, TLB entries, and other resources to multiple VPEs on the same processor can be performed in a special processor configuration state. By default, one VPE of each processor enters its reset vector as if it were a standard MIPS32 core.

# MIPS® MT Multithreaded Execution and Exception Model

#### 2.1 Multithreaded Execution

The MIPS Multithreading ASE does not impose any particular implementation or scheduling model on the execution of parallel threads and VPEs. Scheduling may be round-robin, time-sliced to an arbitrary granularity, or simultaneous. An implementation must not, however, allow a thread which is blocked or suspended by an external or software dependency to monopolize any shared processor resource which could produce a hardware deadlock.

## 2.2 MIPS® MT Exception Model

Multiple threads executing on a single VPE all share the same system coprocessor, the same TLB and the same virtual address space. Each TC has an independent Kernel/Supervisor/User state and ASID for the purposes of instruction decode and memory access. When an exception of any kind is taken, all TCs of the affected VPE other than the one taking the exception are stopped and suspended until the EXL and ERL bits of the Status word are cleared, or, in the case of an EJTAG Debug exception, the Debug state is exited. Debug exceptions have the broader effect of suspending the TCs of other VPEs of the processor as well. See Section 1.3 "Debug Exception Handling". All sources of additional synchronous exceptions must be quiesced before the exception handler begins execution. If simultaneous exception conditions occur across multiple threads, only a single exception, one with the highest relative priority, will be dispatched to a handler. The others will be deferred until EXL/ERL or the Debug state are cleared, and the associated instructions replayed.

Exception handlers for synchronous exceptions caused by the execution of an instruction stream, such as TLB miss and floating-point exceptions, are executed using the GPRs of the TC associated with the instruction stream, unless they are configured to be executed using a Shadow Register Set. When an unmasked asynchronous exception, such as an interrupt, is raised to a VPE, it is implementation dependent which eligible TC is used to execute the exception handler, but TCs can be selectively exempted from use by asynchronous exception handlers.

Imprecise, synchronous exceptions are not permitted on a MIPS MT processor. All exceptions are either precise and synchronous, or asynchronous.

Each exception is associated with an activated TC, even if shadow register sets are used to run the exception handler. This associated TC is referenced whenever a SRSCtl PSS value of 0 is used by RDPGPR and WRPGPR instructions executed by the exception handler.

# 2.3 New Exception Conditions

The Multithreading ASE introduces 6 new exception conditions.

• A Thread Overflow condition, where a TC allocation request cannot be satisfied.

- A Thread Underflow condition, where the termination and deallocation of a thread leaves no dynamically allocatable TCs activated on a VPE.

- An Invalid Qualifier condition, where a YIELD instruction specifies an invalid condition for resuming execution.

- A Gating Storage exception condition, where implementation-dependent logic associated with gating or inter-thread communication (ITC) storage requires software intervention.

- A YIELD Scheduler exception condition, where a valid YIELD instruction would have caused a rescheduling of a TC, and the YIELD Intercept bit is set.

- A GS Scheduler exception, where a Gating Storage load or store would have blocked and caused a rescheduling

of a TC, and the GS Intercept bit is set.

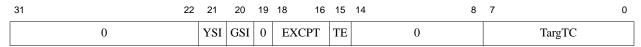

These exception conditions are mapped to a single new *Thread* exception. They can be distinguished based on the CPO *VPEControl EXCPT* field value when the exception is raised.

# 2.4 New Exception Priority

The Thread exception groups together a number of possible exception conditions which can be detected at different stages of a processor pipeline. Thus, different Thread exception conditions may have different priorities relative to other MIPS32 exceptions. The following table describes where Thread exceptions fit in to the MIPS32 priority scheme.

Table 2.1 Priority of Exceptions in MIPS® MT

| Exception                   | Description                                                                                                                                                                        | Туре                 |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Reset                       | The Cold Reset signal was asserted to the processor                                                                                                                                | Asynchronous         |  |  |

| Soft Reset                  | The Reset signal was asserted to the processor                                                                                                                                     | Reset                |  |  |

| Debug Single Step           | An EJTAG Single Step occurred. Prioritized above other exceptions, including asynchronous exceptions, so that one can single-step into interrupt (or other asynchronous) handlers. | Synchronous<br>Debug |  |  |

| Debug Interrupt             | An EJTAG interrupt (EjtagBrk or DINT) was asserted.                                                                                                                                | Asynchronous         |  |  |

| Imprecise Debug Data Break  | An imprecise EJTAG data break condition was asserted.                                                                                                                              | Debug                |  |  |

| Nonmaskable Interrupt (NMI) | The NMI signal was asserted to the processor.                                                                                                                                      | Asynchronous         |  |  |

| Machine Check               | An internal inconsistency was detected by the processor.                                                                                                                           |                      |  |  |

| Interrupt                   | An enabled interrupt occurred.                                                                                                                                                     |                      |  |  |

| Deferred Watch              | A watch exception, deferred because EXL was one when the exception was detected, was asserted after EXL went to zero.                                                              |                      |  |  |

| Debug Instruction Break     | An EJTAG instruction break condition was asserted. Prioritized above instruction fetch exceptions to allow break on illegal instruction addresses.                                 | Synchronous<br>Debug |  |  |

Table 2.1 Priority of Exceptions in MIPS® MT (Continued)

| Exception                         | Description                                                                                                                                                                                                                                                                                                 | Туре                 |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Watch - Instruction fetch         | A watch address match was detected on an instruction fetch. Prioritized above instruction fetch exceptions to allow watch on illegal instruction addresses.                                                                                                                                                 | Synchronous          |

| Address Error - Instruction fetch | A non-word-aligned address was loaded into PC.                                                                                                                                                                                                                                                              |                      |

| TLB Refill - Instruction fetch    | A TLB miss occurred on an instruction fetch.                                                                                                                                                                                                                                                                |                      |

| TLB Invalid - Instruction fetch   | The valid bit was zero in the TLB entry mapping the address referenced by an instruction fetch.                                                                                                                                                                                                             |                      |

| Cache Error - Instruction fetch   | A cache error occurred on an instruction fetch.                                                                                                                                                                                                                                                             |                      |

| Bus Error - Instruction fetch     | A bus error occurred on an instruction fetch.                                                                                                                                                                                                                                                               |                      |

| SDBBP                             | An EJTAG SDBBP instruction was executed.                                                                                                                                                                                                                                                                    | Synchronous<br>Debug |

| Instruction Validity Exceptions   | An instruction could not be completed because it was not allowed access to the required resources, or was illegal: Coprocessor Unusable, Reserved Instruction. If both exceptions occur on the same instruction, the Coprocessor Unusable Exception takes priority over the Reserved Instruction Exception. | Synchronous          |

| Execution Exception               | An instruction-based exception occurred: Integer overflow, trap, system call, breakpoint, floating point, coprocessor 2 exception.  The Overflow, Underflow, Invalid Qualifier, and YIELD Scheduler cases of Thread Exceptions are all Execution Exceptions.                                                |                      |

| Precise Debug Data Break          | A precise EJTAG data break on load/store (address match only) or a data break on store (address+data match) condition was asserted. Prioritized above data fetch exceptions to allow break on illegal data addresses.                                                                                       | Synchronous<br>Debug |

| Watch - Data access               | A watch address match was detected on the address referenced by a load or store. Prioritized above data fetch exceptions to allow watch on illegal data addresses.                                                                                                                                          | Synchronous          |

| Address error - Data access       | An unaligned address, or an address that was inaccessible in the current processor mode was referenced, by a load or store instruction                                                                                                                                                                      |                      |

| TLB Refill - Data access          | A TLB miss occurred on a data access                                                                                                                                                                                                                                                                        |                      |

| TLB Invalid - Data access         | The valid bit was zero in the TLB entry mapping the address referenced by a load or store instruction                                                                                                                                                                                                       |                      |

| TLB Modified - Data access        | The dirty bit was zero in the TLB entry mapping the address referenced by a store instruction                                                                                                                                                                                                               |                      |

| Cache Error - Data access         | A cache error occurred on a load or store data reference                                                                                                                                                                                                                                                    | Synchronous          |

| Bus Error - Data access           | A bus error occurred on a load or store data reference                                                                                                                                                                                                                                                      | or<br>Asynchronous   |

| Thread - GS Scheduler             | A blocking access to Gating Storage was detected with GS Scheduler Intercept enabled                                                                                                                                                                                                                        | Synchronous          |

| Thread - Gating Storage           | Gating Storage has indicated an exception condition                                                                                                                                                                                                                                                         | Synchronous          |

| Precise Debug Data Break          | A precise EJTAG data break on load (address+data match only) condition was asserted. Prioritized last because all aspects of the data fetch must complete in order to do data match.                                                                                                                        | Synchronous<br>Debug |

## 2.5 Interrupts

In general, the binding of hardware interrupts to VPEs is implementation dependent. Interrupt inputs to a processor may be presented in common to all VPEs, leaving it up to software whether any or all VPEs enable and service a given interrupt. A processor may also provide distinct interrupt signals per supported VPE, and/or extend the External Interrupt Controller (EIC) interface to express a VPE identifier in addition to the Exception Vector Offset and Shadow Set Number.

The exception to the above is the hardware interrupt generated by the Count/Compare registers. This logic must be replicated per-VPE, and interrupt events associated with the Count/Compare values of a specific VPE result in interrupt requests only to that VPE.

Depending on the implementation, Performance Counter interrupts may be local to a VPE or "broadcast" to all VPEs of a processor.

Software interrupts IP1 and IP0 must by default be local to a VPE.

## 2.6 Bus Error Exceptions

Bus error exceptions on instruction fetch (IBE) in a MIPS MT processor are synchronous and must be precise as per Section 2.2 "MIPS® MT Exception Model". Bus errors on load/store operations (DBE) are considered to be imprecise and are therefore non-maskable asynchronous exceptions delivered to the VPE where the operation was issued. A DBE exception may thus be taken by a TC other than the one which issued the failing operation. A per-TC TBE bit is defined to allow exception handlers to determine which TC(s) were associated with the failed bus transaction (see Section 4.13 "TCBind Register (CP0 Register 2, Select 2)").

If a DBE results from an operation that was combined across VPEs, a DBE exception must be delivered to all VPEs affected. Where the origin of the failure cannot be determined, all VPEs in a processor must take a DBE exception.

Implementations may provide additional bus error diagnostic information in implementation-dependent CP0 register fields. The DBE state, including the per-TC TBE state, should be analyzed in the context of this information.

# 2.7 Cache Error Exceptions

Cache memories may be shared between multiple VPEs on a virtual multiprocessor. In the event of a cache parity or other data integrity error, all VPEs sharing the cache may be affected, and all must take a Cache Error exception. It is the responsibility of software to coordinate any diagnostics or re-initialization of the shared cache, communicating by means other than cached storage.

# 2.8 EJTAG Debug Exceptions

EJTAG Debug exceptions override MIPS MT scheduling and TC management. See Section 1.3 "Debug Exception Handling".

# 2.9 Shadow Register Sets

MIPS MT optionally allows TCs to be assigned for use as Shadow Register Set (SRS) storage. This is accomplished by writing the TC number into a programmable field of one of the *SRSConf* registers (see Section 4.19 "SRSConf0 (CP0 Register 6, Select 1)"). A TC assigned for use as SRS storage must never be Activated, nor may it be pro-

12 MIPS32® Architecture for Programmers VolumeIV-f: The MIPS® MT Application-Specific Extension to the MIPS32® Architecture, Revision 1.04

| и | rammed to be Dynamically Allocatable. Because SRS management and control is performed on a per-VPE basis, with only a single SRSCtl register per VPE, multithreading should never be explicitly re-enabled in an exception han ler which executes using an SRS. |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

|   |                                                                                                                                                                                                                                                                 |

| MIP  | S® MT Multithreaded Execution and Exception Model                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

|      |                                                                                                                    |

| 14 I | MIPS32® Architecture for Programmers VolumeIV-f: The MIPS® MT Application-Specific Extension to the MIPS32® Archi- |

tecture, Revision 1.04

# **MIPS® MT Instructions**

## 3.1 New Instructions

The MIPS MT ASE contains 8 new instructions.

**FORK** and **YIELD** control thread allocation, deallocation, and scheduling, and are available in all execution modes if implemented and enabled.

**MFTR** and **MTTR** are system coprocessor (Cop0) instructions available to privileged system software for managing thread state.

**EMT** and **DMT** are privileged Cop0 instructions for enabling and disabling multithreaded operation of a VPE.

EVPE and DVPE are privileged Cop0 instructions for enabling and disabling multi-VPE operation of a processor.

These instructions will cause a **Reserved Instruction** exception if executed by a processor not implementing the MIPS MT ASE.

Format: DMT DMT rt

Purpose: Disable Multi-Threaded Execution

To return the previous value of the VPEControl register (see section 4.5) and disable multi-threaded execution. If DMT is specified without an argument, GPR r0 is implied, which discards the previous value of the VPEControl register.

**Description:** GPR[rt]  $\leftarrow$  VPEControl; VPEControl<sub>TE</sub>  $\leftarrow$  0

The current value of the *VPEControl* register is loaded into general register *rt*. The Threads Enable (*TE*) bit in the *VPEControl* register is then cleared, suspending concurrent execution of instruction streams other than that which issues the DMT. This is independent of any per-TC halted state.

#### **Restrictions:**

If access to Coprocessor 0 is not enabled, a Coprocessor Unusable Exception is signaled.

In implementations that do not implement the MT ASE, this instruction results in a Reserved Instruction Exception.

#### Operation:

This operation specification is for the general multi-threading enable/disable operation, with the sc (set/clear) field as a variable. The individual instructions EMT and DMT have a specific value for the sc field.

```

\begin{array}{l} \text{data} \leftarrow \text{VPEControl} \\ \text{GPR[rt]} \leftarrow \text{data} \\ \text{VPEControl}_{\text{TE}} \leftarrow \text{sc} \end{array}

```

#### **Exceptions:**

Coprocessor Unusable

Reserved Instruction (Implementations that do not include the MT ASE )

#### **Programming Notes:**

The effects of this instruction are identical to those accomplished by the sequence of reading *VPEControl* into a GPR, clearing the *TE* bit to create a temporary value in a second GPR, and writing that value back to *VPEControl*. Unlike the multiple instruction sequence, however, the DMT instruction does not consume a temporary register, and can not be aborted in the middle by an interrupt or exception.

The effect of a DMT instruction may not be instantaneous. An instruction hazard barrier, e.g. JR.HB, is required to guarantee that all other threads have been suspended. If a DMT instruction is followed in the same instruction stream by a MFC0 or MFTR from the *VPEControl* register, a JALR.HB, JR.HB, EHB, or ERET instruction must be issued between the DMT and the read of *VPEControl* to guarantee that the new state of *TE* will be picked up by the read.

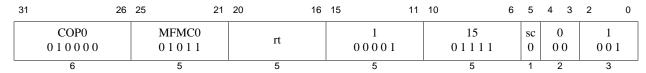

| 31                  | 26 | 25           | 21 | 20 | 16 | 15 | 11                                                 | 10 |                                                    | 6 | 5       | 4 | 3 | 2   | 0     |

|---------------------|----|--------------|----|----|----|----|----------------------------------------------------|----|----------------------------------------------------|---|---------|---|---|-----|-------|

| COP0<br>0 1 0 0 0 0 |    | MFM<br>0 1 0 |    |    | rt |    | $\begin{smallmatrix}0\\0&0&0&0&0\end{smallmatrix}$ |    | $\begin{smallmatrix}0\\0&0&0&0&0\end{smallmatrix}$ |   | sc<br>0 | 0 |   | 0 ( | 1 ) 1 |

| 6                   |    | 5            |    |    | 5  |    | 5                                                  |    | 5                                                  |   | 1       | 2 |   |     | 3     |

Format: DVPE MIPS MT

DVPE rt

Purpose: Disable Virtual Processor Execution

To return the previous value of the *MVPControl* register (see section 4.2) and disable multi-VPE execution. If DVPE is specified without an argument, GPR *r0* is implied, which discards the previous value of the *MVPControl* register.

```

Description: GPR[rt] \leftarrow MVPControl; MVPControl<sub>EVP</sub> \leftarrow 0

```

The current value of the *MVPControl* register is loaded into general register *rt*. The Enable Virtual Processors (*EVP*) bit in the *MVPControl* register is then cleared, suspending concurrent execution of instruction streams other than that which issues the DVPE.

#### Restrictions:

If access to Coprocessor 0 is not enabled, a Coprocessor Unusable Exception is signaled.

If the VPE executing the instruction is not a Master VPE, with the MVP bit of the VPEConf0 register set, the EVP bit is unchanged by the instruction.

In implementations that do not implement the MT ASE, this instruction results in a Reserved Instruction Exception.

#### Operation:

This operation specification is for the general VPE enable/disable operation, with the *sc* (set/clear) field as a variable. The individual instructions EVPE and DVPE have a specific value for the *sc* field.

```

\label{eq:data} \begin{array}{l} \mbox{data} \leftarrow \mbox{MVPControl} \\ \mbox{GPR[rt]} \leftarrow \mbox{data} \\ \mbox{if}(\mbox{VPEConf0}_{\mbox{MVP}} = 1) \mbox{ then} \\ \mbox{MVPControl}_{\mbox{EVP}} \leftarrow \mbox{sc} \\ \mbox{endif} \end{array}

```

#### **Exceptions:**

Coprocessor Unusable

Reserved Instruction (Implementations that do not include the MT ASE)

#### **Programming Notes:**

The effects of this instruction are identical to those accomplished by the sequence of reading *MVPControl* into a GPR, clearing the *EVP* bit to create a temporary value in a second GPR, and writing that value back to *MVPControl*. Unlike the multiple instruction sequence, however, the DVPE instruction does not consume a temporary register, and can not be aborted in the middle by an interrupt or exception, nor by the scheduling of a different instruction stream.

The effect of a DVPE instruction may not be instantaneous. An instruction hazard barrier, e.g. JR.HB, is required to guarantee that all other TCs have been suspended.

If a DVPE instruction is followed in the same instruction stream by a MFC0 or MFTR from the *MVPControl* register, a JALR.HB, JR.HB, EHB, or ERET instruction must be issued between the DVPE and the read of *MVPControl* to guarantee that the new state of *EVP* will be picked up by the read.

| 31 | 26                  | 25 21              | 20 16 | 15 11       | 10 6            | 5       | 4 3      | 2 0                                            |  |

|----|---------------------|--------------------|-------|-------------|-----------------|---------|----------|------------------------------------------------|--|

|    | COP0<br>0 1 0 0 0 0 | MFMC0<br>0 1 0 1 1 | rt    | 1 0 0 0 0 1 | 15<br>0 1 1 1 1 | sc<br>1 | 0<br>0 0 | $\begin{smallmatrix}1\\0&0&1\end{smallmatrix}$ |  |

|    | 6                   | 5                  | 5     | 5           | 5               | 1       | 2        | 3                                              |  |

Format: EMT EMT rt

Purpose: Enable Multi-Threaded Execution

To return the previous value of the *VPEControl* register (see section 4.5) and enable multi-threaded execution. If EMT is specified without an argument, GPR *r0* is implied, which discards the previous value of the *VPEControl* register.

**Description:** GPR[rt]  $\leftarrow$  VPEControl; VPEControl<sub>TE</sub>  $\leftarrow$  1

The current value of the *VPEControl* register is loaded into general register *rt*. The Threads Enable (*TE*) bit in the *VPEControl* register is then set, allowing multiple instruction streams to execute concurrently.

#### **Restrictions:**

If access to Coprocessor 0 is not enabled, a Coprocessor Unusable Exception is signaled.

In implementations that do not implement the MT ASE, this instruction results in a **Reserved Instruction Exception**.

#### Operation:

This operation specification is for the general multi-threading enable/disable operation, with the sc (set/clear) field as a variable. The individual instructions EMT and DMT have a specific value for the sc field.

```

\begin{array}{l} \text{data} \leftarrow \text{VPEControl} \\ \text{GPR[rt]} \leftarrow \text{data} \\ \text{VPEControl}_{\text{TE}} \leftarrow \text{sc} \end{array}

```

#### **Exceptions:**

Coprocessor Unusable

Reserved Instruction (Implementations that do not include the MT ASE)

#### **Programming Notes:**

The effects of this instruction are identical to those accomplished by the sequence of reading *VPEControl* into a GPR, setting the *TE* bit to create a temporary value in a second GPR, and writing that value back to *VPEControl*. Unlike the multiple instruction sequence, however, the EMT instruction does not consume a temporary register, and can not be aborted in the middle by an interrupt or exception.

If an EMT instruction is followed in the same instruction stream by a MFC0 or MFTR from the *VPEControl* register, a JALR.HB, JR.HB, EHB, or ERET instruction must be issued between the EMT and the read of *VPEControl* to guarantee that the new state of *TE* will be picked up by the read.

| 31                  | 26 | 25 | 21                 | 20 | 16 | 15 | 11                                                 | 10 | )                                                  | 6 | 5       | 4 | 3 | 2 | 0        |

|---------------------|----|----|--------------------|----|----|----|----------------------------------------------------|----|----------------------------------------------------|---|---------|---|---|---|----------|

| COP0<br>0 1 0 0 0 0 |    |    | MFMC0<br>0 1 0 1 1 |    | rt |    | $\begin{smallmatrix}0\\0&0&0&0&0\end{smallmatrix}$ |    | $\begin{smallmatrix}0\\0&0&0&0&0\end{smallmatrix}$ |   | sc<br>1 | 0 |   | 0 | 1<br>0 1 |

| 6                   |    |    | 5                  |    | 5  |    | 5                                                  |    | 5                                                  |   | 1       | 2 | 2 |   | 3        |

Format: EVPE EVPE rt

Purpose: Enable Virtual Processor Execution

To return the previous value of the *MVPControl* register (see section 4.2) and enable multi-VPE execution. If EVPE is specified without an argument, GPR r0 is implied, which discards the previous value of the *MVPControl* register.

**Description:** GPR[rt]  $\leftarrow$  MVPControl; MVPControl<sub>EVP</sub>  $\leftarrow$  1

The current value of the *MVPControl* register is loaded into general register *rt*. The Enable Virtual Processors (*EVP*) bit in the *MVPControl* register is then set, enabling concurrent execution of instruction streams on all non-inhibited Virtual Processing Elements (VPEs) on a processor.

#### Restrictions:

If access to Coprocessor 0 is not enabled, a Coprocessor Unusable Exception is signaled.

If the VPE executing the instruction is not a Master VPE, with the MVP bit of the VPEConf0 register set, the EVP bit is unchanged by the instruction.

In implementations that do not implement the MT ASE, this instruction results in a Reserved Instruction Exception.

#### **Operation:**

This operation specification is for the general VPE enable/disable operation, with the *sc* (set/clear) field as a variable. The individual instructions EVPE and DVPE have a specific value for the *sc* field.

```

\label{eq:data} \begin{array}{l} \mbox{data} \leftarrow \mbox{MVPControl} \\ \mbox{GPR[rt]} \leftarrow \mbox{data} \\ \mbox{if}(\mbox{VPEConf0}_{\mbox{MVP}} = 1) \mbox{ then} \\ \mbox{MVPControl}_{\mbox{EVP}} \leftarrow \mbox{sc} \\ \mbox{endif} \end{array}

```

#### **Exceptions:**

Coprocessor Unusable

Reserved Instruction (Implementations that do not include the MT ASE)

#### **Programming Notes:**

The effects of this instruction are identical to those accomplished by the sequence of reading *MVPControl* into a GPR, setting the *EVP* bit to create a temporary value in a second GPR, and writing that value back to *MVPControl*. Unlike the multiple instruction sequence, however, the EVPE instruction does not consume a temporary register, and can not be aborted in the middle by an interrupt or exception, nor by the scheduling of a different instruction stream.

If an EVPE instruction is followed in the same instruction stream by a MFC0 or MFTR from the *MVPControl* register, a JALR.HB, JR.HB, EHB, or ERET instruction must be issued between the EVPE and the read of *MVPControl* to guarantee that the new state of *EVP* will be picked up by the read.

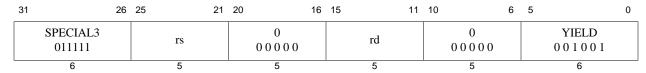

| 31                 | 26 | 25 | 21 | 20 | 16 | 15 | 11 | 10        | 6 | 5 |                     | 0 |

|--------------------|----|----|----|----|----|----|----|-----------|---|---|---------------------|---|

| SPECIAL3<br>011111 |    | rs |    | rt |    |    | rd | 0 0 0 0 0 |   |   | FORK<br>0 0 1 0 0 0 |   |

| 6                  |    | 5  |    | 5  |    |    | 5  | 5         |   |   | 6                   |   |

Format: FORK rd, rs, rt MIPS MT

Purpose: Allocate and Schedule a New Thread

To cause a thread context to be allocated and associated with a new instruction stream.

Description: NewThread's GPR[rd]  $\leftarrow$  GPR[rt], NewThread's TCRestart  $\leftarrow$  GPR[rs]

The FORK instruction causes a free dynamically allocatable thread context (TC) to be allocated and activated on the issuing VPE. It takes two operand values from GPRs. The *rs* value is used as the starting fetch address and execution mode for the new thread. The *rt* value is copied into GPR *rd* of the new TC. The *TCStatus* register of the new TC is set up as a function of the FORKing TC as described in section 4.12. If the *UserLocal* register is implemented, the *UserLocal* value of the FORKing TC is also copied to the new TC. The newly allocated TC will begin executing instructions according to the implemented scheduling policy if and when multi-threaded execution is otherwise enabled.

#### **Restrictions:**

If no free, non-halted, dynamically allocatable TC is available for the fork, a Thread Exception is raised for the FORK instruction, with the *VPEControl.EXCPT* CP0 register field set to 1 to indicate the Thread Overflow case.

Processors which implement only a single TC per VPE may implement FORK by simply raising the Thread Exception and indicating the Overflow.

Any exceptions associated with the virtual address passed in rs will be taken by the new thread of execution.

#### Operation:

```

success \leftarrow 0

for t in 0...MVPConf0_{PTC}

if TC[t].TCBind_{CurVPE} = TCBind_{CurVPE} then

if (TC[t].TCStatus_{DA} = 1)

and (TC[t].TCHalt^{H} = 0)

and (TC[t].TCStatus_A = 0)

and (success = 0) then

TC[t].TCRestart \leftarrow GPR[rs]

TC[t].GPR[rd] \leftarrow GPR[rt]

if (Config3_{ULRI} = 1) then

TC[t].UserLocal \leftarrow UserLocal

endif

activated \leftarrow 1

priorcu \leftarrow TC[t].TCStatus_{TCU3..TCU0}

priormx \leftarrow TC[t].TCStatus_{TMX}

priorixmt \leftarrow TC[t].TCStatus_{IXMT}

TC[t].TCStatus = priorcu || priormx || 0<sup>6</sup> || 1 || ImpDep<sup>4</sup>

| | 1 | | 0 | | activated| | Status<sub>KSU</sub> | | priorixmt

| | 0^2 | | TCStatus<sub>TASID</sub>

success \leftarrow 1

endif

endif

endfor

if success = 0

VPEControl_{EXCPT} \leftarrow 1

```

SignalException(Thread)

endif

#### **Exceptions:**

Reserved Instruction Thread

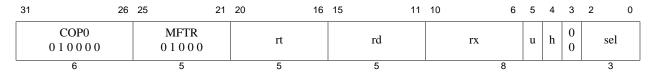

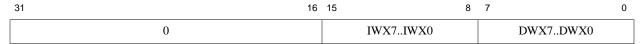

Format: MFTR rd, rt, u, sel, h MIPS MT

See also the *Idiom(s)* column of Table 3.1.

Purpose: Move from Thread Context

To move the contents of a register within a targeted thread context or VPE into a general register of the current thread.

**Description:**  $GPR[rd] \leftarrow TC[VPEControl_{TargTC}][u,rt,sel,h]$

The contents of the register specified are loaded into general register *rd*. The target context to be read is determined by the value of the TargTC field of the CP0 *VPEControl* register (see section 4.5). The register to be read within the selected context is determined by the value in the *rt* operand register, in conjunction with the *u* and *sel* bits of the MFTR instruction, according to table Table 3.1. If the register to be read is instantiated per-processor or per-VPE, rather than per-TC, the register selected is that of the processor within which the target TC is instantiated, or the VPE to which the target TC is bound (see section 4.13), respectively. The encoding is the same as for MTTR, except that it is *rt* and not *rd* that is used to identify the target in the move-from case.

Coprocessor 1 and 2 registers and DSP accumulators referenced by the MFTR instruction are those bound to the target TC. The *TCUx* bits and *TMX* bit of the target TC's *TCStatus* register are ignored.

If the selected register is not implemented on the processor, or otherwise not accessible to the TC that issued the MFTR, as in the case of references to TCs and coprocessor resources bound to other VPEs when the VPE executing the MFTR does not have MVP set in VPConfig0, the resulting rd value is -1.

The *Idiom*(*s*) column in Table 3.1 specifies the assembler idiom that is used to express an access to the particular register.

u Value

sel Value

Register Selected

Idiom(s)

0

n

Coprocessor 0 Register number rt, sel = sel MFTC0 rd, rt

t MFTC0 rd, rt, sel

t t MFTGPR rd, rt

**Table 3.1 MFTR Source Decode**

**Table 3.1 MFTR Source Decode (Continued)**

| u Value | sel Value |              | Register Selected                                                                             | ldiom(s)       |

|---------|-----------|--------------|-----------------------------------------------------------------------------------------------|----------------|

| 1       | 1         | rt Value     | Selection                                                                                     |                |

|         |           | 0            | Lo Register / Lo component of DSP Accumulator 0                                               | MFTLO rd       |

|         |           |              |                                                                                               | MFTLO rd, ac0  |

|         |           | 1            | Hi Register / Hi component of DSP Accumulator 0                                               | MFTHI rd       |

|         |           |              |                                                                                               | MFTHI rd, ac0  |

|         |           | 2            | ACX Register / ACX component of Accumulator 0                                                 | MFTACX rd      |

|         |           |              |                                                                                               | MFTACX rd, ac0 |

|         |           | 4            | Lo component of DSP Accumulator 1                                                             | MFTLO rd, ac1  |

|         |           | 5            | Hi component of DSP Accumulator 1                                                             | MFTHI rd, ac1  |

|         |           | 6            | Reserved for ACX of DSP Accumulator 1                                                         | MFTACX rd, ac1 |

|         |           | 8            | Lo component of DSP Accumulator 2                                                             | MFTLO rd, ac2  |

|         |           | 9            | Hi component of DSP Accumulator 2                                                             | MFTHI rd, ac2  |

|         |           | 10           | Reserved for ACX of DSP Accumulator 2                                                         | MFTACX rd, ac2 |

|         |           | 12           | Lo component of DSP Accumulator 3                                                             | MFTLO rd, ac3  |

|         |           | 13           | Hi component of DSP Accumulator 3                                                             | MFTHI rd, ac3  |

|         |           | 14           | Reserved for ACX of DSP Accumulator 3                                                         | MFTACX rd, ac3 |

|         |           | 16           | DSPControl register                                                                           | MFTDSP rd      |

|         |           | Other Values | of rt, Reserved, Unpredictable                                                                |                |

| 1       | 2         |              | FPR[rt]                                                                                       | MFTC1 rd, ft   |

|         |           |              |                                                                                               | MFTHC1 rd, ft  |

| 1       | 3         |              | FPCR[rt]                                                                                      | CFTC1 rd, ft   |

| 1       | 4         |              | ], where $n$ is composed by concatenating $rx$ with $rt$ , ding the most significant bits.    |                |

| 1       | 5         |              | l[n], where $n$ is composed by concatenating $rx$ with $rt$ , ding the most significant bits. |                |

| 1       | >5        | Reserved, U  | npredictable                                                                                  |                |

The selected value is written into the target register *rd*. If the precision of the source register is less than the precision of the target GPR, the value is sign-extended.

The h bit of the instruction word selects the high-order half of the source register in instances where the source is a register of greater precision than the target GPR.

#### **Restrictions:**

An MFTR instruction where the target TC is not in a Halted state (i.e. *TCHalt.H* is not set), or where a TC other than the one issuing the MFTR is active in the target VPE on a reference to a per-VPE CP0 register, may result in an

MIPS32® Architecture for Programmers VolumeIV-f: The MIPS® MT Application-Specific Extension to the MIPS32® Architecture, Revision 1.04

UNSTABLE value.

#### Operation:

```

\text{if VPEConf0}_{MVP} = 0 \text{ and } ( \text{ TC[VPEControl}_{\text{TargTC}}]. \\ \text{TCBind}_{\text{CurVPE}} \neq \\ \text{TCBind}_{\text{CurVPE}} ) \text{ then } \\

data \leftarrow -1

else if VPEControl_{TargTC} > MVPConf0_{PTC} then

data \leftarrow -1

else if u = 0 then

\texttt{data} \leftarrow \texttt{TC[VPEControl}_{\texttt{TargTC}}].\texttt{CPR[0,rt,sel]}

else

case sel

0: data \leftarrow \texttt{TC[VPEControl}_{\texttt{TargTC}}].\texttt{GPR[rt]}

1: case rt

0: data \leftarrow TC[VPEControl_{TargTC}].Lo

1: data ← TC[VPEControl<sub>TargTC</sub>].Hi

2: data \leftarrow TC[VPEControl_{TargTC}].ACX

4: \; \mathtt{data} \; \leftarrow \; \mathtt{TC}[\mathtt{VPEControl}_{\mathtt{TargTC}}] \, . \mathtt{DSPLo}[1]

5: data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].\text{DSPHi[1]}

6: data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].DSPACX[1]

8: data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].DSPLo[2]

9: data \leftarrow \texttt{TC[VPEControl}_{\texttt{TargTC}}].\texttt{DSPHI[2]}

10: data \leftarrow TC[VPEControl_{TargTC}].DSPACX[2]

12 data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].DSPLo[3]

13: \texttt{data} \leftarrow \texttt{TC[VPEControl}_{\texttt{TargTC}}]. \texttt{DSPHi[3]}

14: \texttt{data} \leftarrow \texttt{TC[VPEControl}_{\texttt{TargTC}}].\texttt{DSPACX[3]}

16: data \leftarrow TC[VPEControl_{TargTC}].DSPControl

otherwise: data \leftarrow UNPREDICTABLE

2: data \leftarrow TC[VPEControl_{TargTC}].FPR[rt]

3: data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].\text{FPCR[rt]}

4: data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].\text{CP2CPR[rx||rt]}

5: data \leftarrow \text{TC[VPEControl}_{\text{TargTC}}].\text{CP2CCR[rx||rt]}

otherwise: data ← UNPREDICTABLE

endif

if h = 1 then

data \leftarrow data_{63..32}

endif

GPR[rd] \leftarrow data_{31..0}

```

#### **Exceptions:**

Coprocessor Unusable Reserved Instruction Move to Thread Context MTTR

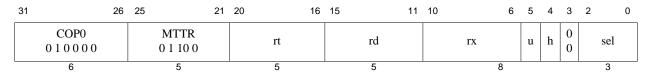

Format: MTTR rt, rd, u, sel, h

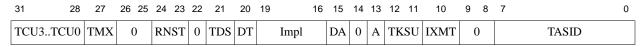

See also Idiom(s) column of Table 3.2.

**Purpose:** Move to Thread Context

To move the contents of a general register of the current thread into a register within a targeted thread context.

**Description:**  $TC[VPEControl_{TargTC}][u,rd,sel,h] \leftarrow GPR[rt]$

The contents of the *rt* register specified are written into a register of an arbitrary thread context (TC) or virtual processor (VPE).